A host of complex problems involve network analysis—everything from how viruses spread in populations, to choosing the most efficient route to go to several points in a network (such as roadways or railways), to calculating the fewest number of mutations needed to transform one string of DNA into another.

To simplify the task of solving these computationally intensive network problems without relying on software, researchers at the National Institute of Technology (NIST) developed electronic hardware that replicates the network’s architecture. Akin to an analog computer, it then applies race logic to rapidly solve a variety of complex puzzles with a minimum expenditure of energy compared to general-purpose computers.

Race logic encodes information differently from a standard computer. Digital information is typically encoded and processed using computer bits, with a “1” indicating a logic statement is true and a “0” indicating it’s false. When a bit flips its value, say from 0 to 1, it means a particular logic operation has been performed to solve a mathematical problem.

In contrast, race logic encodes and processes information by representing it as time signals—that is, the time when a particular group of bits changes, or flips, from 0 to 1. Large numbers of bit flips are the primary reason standard computers use so much energy. Race logic encodes signals encoded in time, which involves only a few bit flips to process information, so it uses much less power than signals encoded as 0s or 1s.

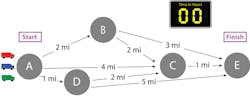

The NIST device then performs computations adding delays to time signals based on the network being analyzed. For example, consider a fleet of trucks at City A that must deliver medicine to City E as quickly as possible, a relatively simple problem. Possible routes go through City B, City C and City D.

To determine the most efficient route, the race-logic hardware evaluates each possible trip segment of the trip, such as A to B and A to D. If A to B takes more time to travel than A to D because it’s a longer path or has more traffic, the hardware assigns A to B a longer delay time. In the team’s hardware, the time delays are made by adding resistance to the slower segment.

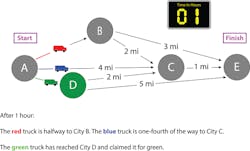

To determine which route to the final destination is fastest, the trucks travel all possible routes through the different intermediate delivery points. So, NIST researchers inserted a group of time-encoded signals at the starting point, each acting as a different driver that goes through the team’s simulated hardware circuit.

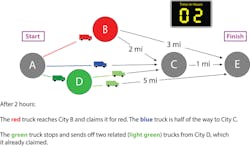

Whenever a driver arrives at an intermediate destination points, the model sends out new drivers (i.e., new time signals) who fan out in different directions to the remaining destinations. If a driver arrives at a destination that another driver has already been to, that driver drops out because their path is no longer competitive. The winner, the first driver to arrive at the end of the circuit, has traveled the shortest route, the solution to the network problem.

Simulations conducted by the NIST team showed that its design, which has not yet been incorporated into a working device, can handle a much broader class of networks and puzzles. These puzzles include finding the best alignment between two proteins or two strings of nucleotides (molecules that form the building blocks of DNA) and determining the shortest path between two destinations on a network.

The NIST team showed how to use memory, which had not been used in previous race-logic devices, to create a more general temporal computer.

About the Author

Voice Your Opinion!

To join the conversation, and become an exclusive member of Machine Design, create an account today!

Leaders relevant to this article: